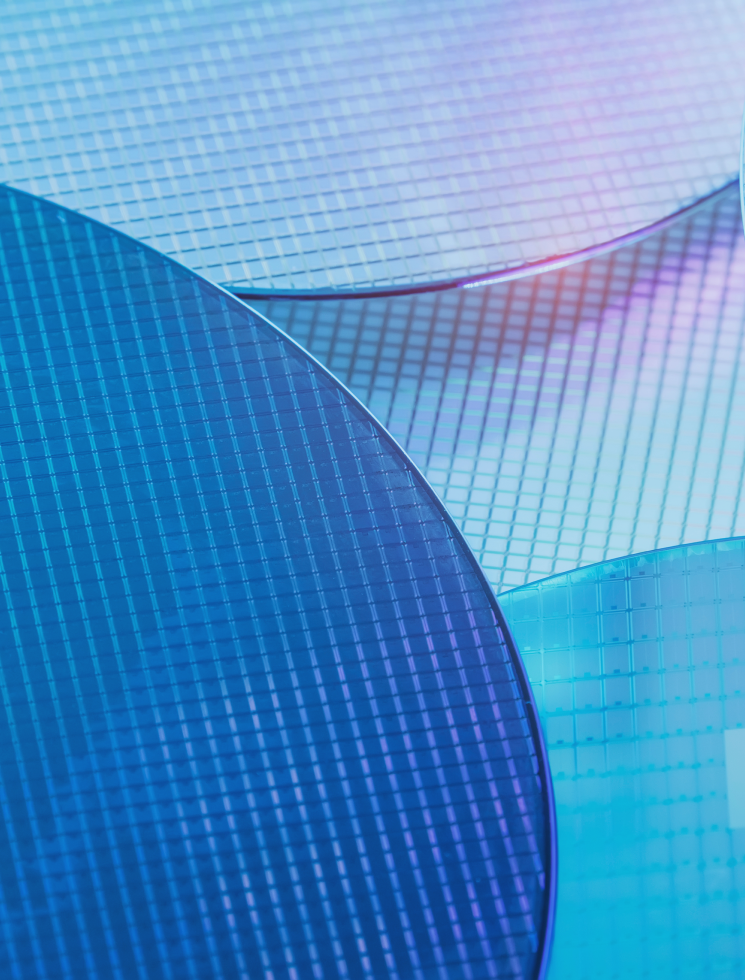

Display IP

クオリタス半導体は、ディスプレイチップセット(Display Chipset)向けHSI IPを多数提供いたします。ディスプレイパネル製品が多様化するにつれ て応用分野も増えており、Display Chipsetも新たな成長エンジンを 獲得しています。4K UHDに次いで8K UHD解像度に対応するディスプレイ 機器の発売に後押しされ、より鮮明な画質と解像度で情報の発信に 取り組んでいます。ディスプレイチップセットの代表例はDTV SoCや TCON IC、DDIであり、高解像度・高画質データを伝送するための超高速 インターフェイスIPとディスプレイチップセットの開発は、 クオリタス半導体の主要課題の一つです。

クオリタス半導体は、TCONインターフェイスの代表的な標準であるeDPと TCON ICにおいて、パネルを駆動するDDIで映像信号を伝送するための Intra-Panelインターフェイスを提供しています。

eDP RX PHY

Request DatasheetThe eDP RX PHY IP is a cost-effective and low-power solution that includes IO pads and ESD structures. With extensive built-in self-test features, including loopback and scan, it ensures robust functionality and easy verification. This hardmacro supports the eDP RX v1.4b and v1.5a standard and is commonly used for connecting a timing controller (TCON) to a host processor.

Features

- Compliant to DisplayPort v1.4, eDP v1.4b, and eDP v1.5a

- Supports data rates from Reduced Bit Rate ( RBR :1.62 Gbps) to High Bit Rate 3

( HBR3 :8.1 Gbps), and user configurable custom B/Ws - Supports for eDP v1.4b features, such as PSR1 and PSR2

- Supports eDP v1.5a features, including AUX-less link training ( Low Frequency Periodic Signaling )

- Adaptive Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Automatic calibration of analog circuits and parametric offset cancellation

- Supports Built in Eye Open Monitor feature

- Built In Self Test (BIST), including DP Standard Training Pattern Sets (TPS1~TPS4), pseudo random bit stream generation and checkers

- Includes PCS layer for easier link interfaces (symbol aligning, 8b10b decoder, de-scrambler, and support for fail-safe auto recovery feature )

- AUX Rx controller includes sync detection and fully synthesizable digital CDR

- Operating parameters can be fully configured by APB v3.0 and SPI interfaces

Tech Specs

| Foundry Node | 14 nm | |

|---|---|---|

| Standard | eDP v1.4b | eDP v1.5a |

| Max. datarate | Under NDA | |

| Status | ||

Intra-Panel TX PHY

Request DatasheetQualitas' Intra-panel TX PHY IP is an advanced chip-on-glass (ACOG) and chip-on-film (COF) transmitter embedded into the timing controller for TFT-LCD panels. This technology enables a single chip to support multiple display interfaces, reducing system costs and complexity. It also provides higher data transfer rates, lower power consumption, and compatibility with a wide range of devices.

Features

- Supports data rates from 120 Mbps to a maximum of 4 Gbps

- Supports Power Down and Low-Power modes during V-blank period

- Programmable differential transmitter output impedance (75 ohm ~ 180 ohm)

- Programmable differential transmitter output amplitude (up to 6 dB)

- Jitter Injector Includes jitter Injector for debugging purposes

- Built-in self-test (BIST) including pseudo random bit stream (PRBS) generation and checker

Tech Specs

| Foundry Node | 28 nm | 14 nm | 8 nm |

|---|---|---|---|

| Standard | Under NDA | ||

| Max. datarate | |||

| Status | |||