Display IP

Qualitas Semiconductor provides various HSI IPs for display chipsets. Display chipsets have been gaining new momentum as they have been diversifying together with display panels. With the release of display devices supporting 8K UHD resolution following 4K UHD, the aim is to deliver sharper image quality and resolution. Representative display chipsets include DTV SoC, TCON IC, and DDI, and the development of high-speed interface IP for transmitting higher resolution and high-quality data is an important task for Qualitas Semiconductor.

Qualitas Semiconductor provides the major TCON interface standards, including eDP and intra-panel interfaces, which transmits video signals from the TCON IC to the DDI running the panel.

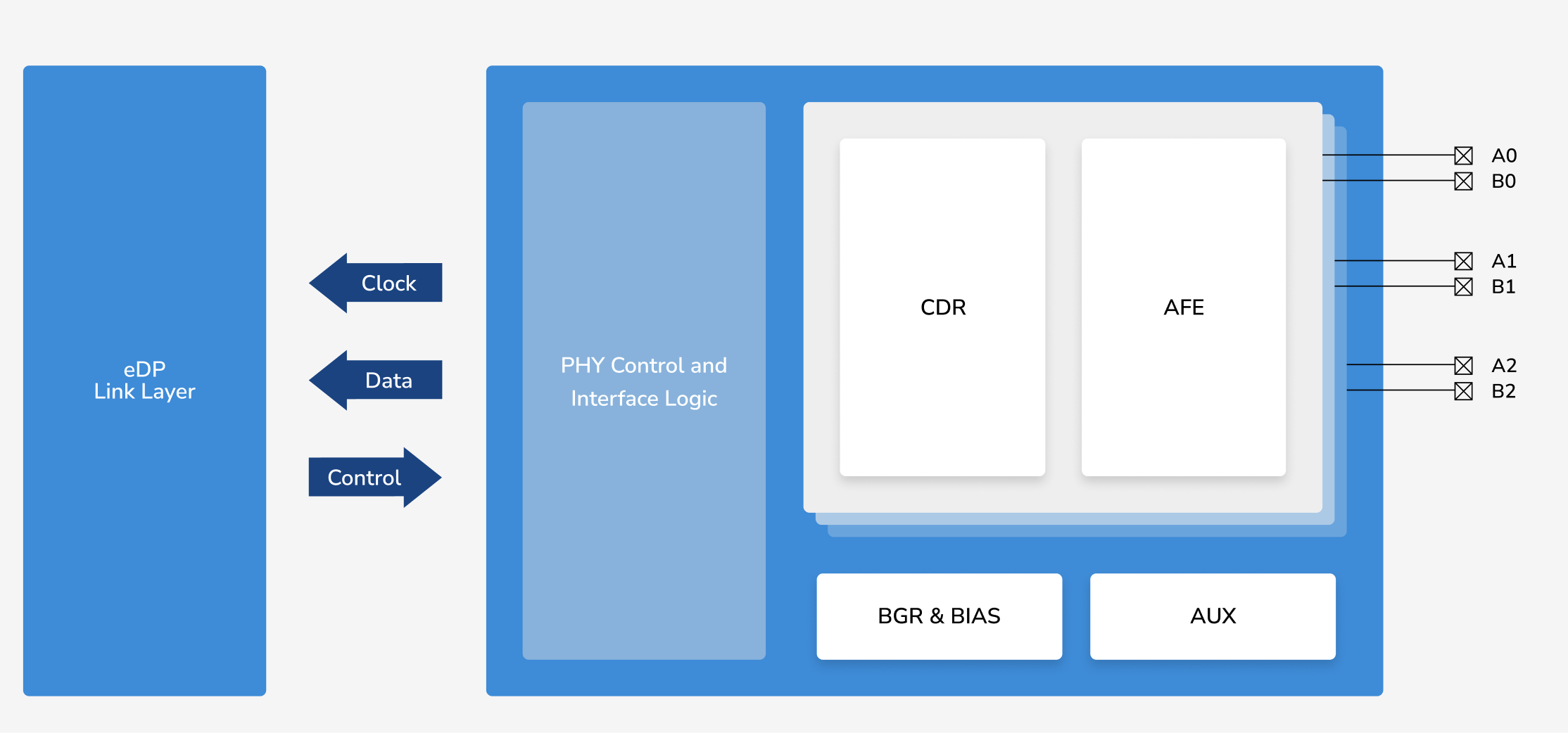

eDP RX PHY

Request DatasheetThe eDP RX PHY IP is a cost-effective and low-power solution that includes IO pads and ESD structures. With extensive built-in self-test features, including loopback and scan, it ensures robust functionality and easy verification. This hardmacro supports the eDP RX v1.4b and v1.5a standard and is commonly used for connecting a timing controller (TCON) to a host processor.

Features

- Compliant to DisplayPort v1.4, eDP v1.4b, and eDP v1.5a

- Supports data rates from Reduced Bit Rate ( RBR :1.62 Gbps) to High Bit Rate 3

( HBR3 :8.1 Gbps), and user configurable custom B/Ws - Supports for eDP v1.4b features, such as PSR1 and PSR2

- Supports eDP v1.5a features, including AUX-less link training ( Low Frequency Periodic Signaling )

- Adaptive Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Automatic calibration of analog circuits and parametric offset cancellation

- Supports Built in Eye Open Monitor feature

- Built In Self Test (BIST), including DP Standard Training Pattern Sets (TPS1~TPS4), pseudo random bit stream generation and checkers

- Includes PCS layer for easier link interfaces (symbol aligning, 8b10b decoder, de-scrambler, and support for fail-safe auto recovery feature )

- AUX Rx controller includes sync detection and fully synthesizable digital CDR

- Operating parameters can be fully configured by APB v3.0 and SPI interfaces

Tech Specs

| Foundry Node | 14 nm | |

|---|---|---|

| Standard | eDP v1.4b | eDP v1.5a |

| Max. datarate | Under NDA | |

| Status | ||

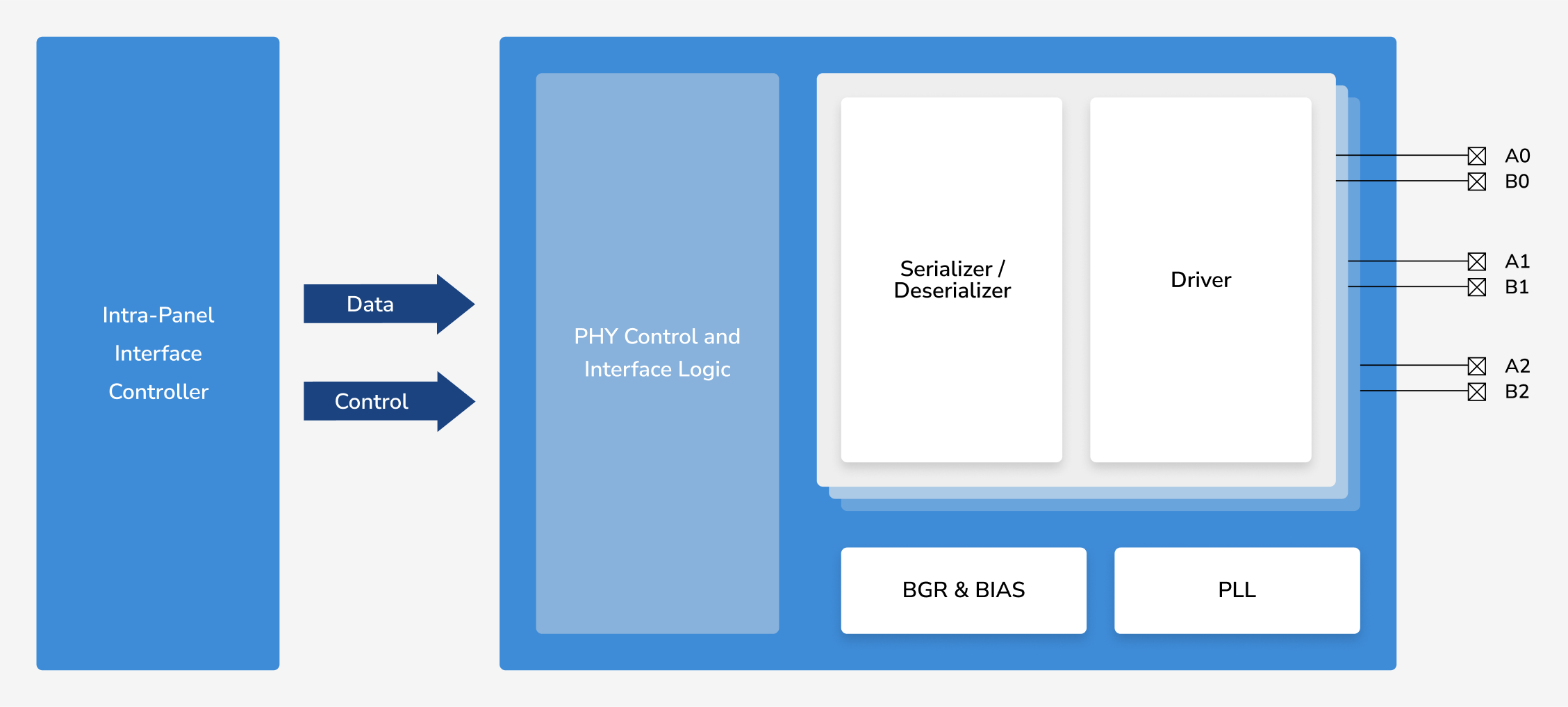

Intra-Panel TX PHY

Request DatasheetQualitas' Intra-panel TX PHY IP is an advanced chip-on-glass (ACOG) and chip-on-film (COF) transmitter embedded into the timing controller for TFT-LCD panels. This technology enables a single chip to support multiple display interfaces, reducing system costs and complexity. It also provides higher data transfer rates, lower power consumption, and compatibility with a wide range of devices.

Features

- Supports data rates from 120 Mbps to a maximum of 4 Gbps

- Supports Power Down and Low-Power modes during V-blank period

- Programmable differential transmitter output impedance (75 ohm ~ 180 ohm)

- Programmable differential transmitter output amplitude (up to 6 dB)

- Jitter Injector Includes jitter Injector for debugging purposes

- Built-in self-test (BIST) including pseudo random bit stream (PRBS) generation and checker

Tech Specs

| Foundry Node | 28 nm | 14 nm | 8 nm |

|---|---|---|---|

| Standard | Under NDA | ||

| Max. datarate | |||

| Status | |||