PCle

Qualitas Semiconductor provides high-speed interconnect technology focusing on PCIe (Peripheral Component Interconnect Express) solutions. The PCIe standard is an interconnect technology for connecting various peripheral devices. As the version number increases, the data transfer speed doubles. The latest version, PCIe 6.0, supports ultra-high-speed transmission reaching up to 64 Gbps. The demand for high bandwidth and low latency communication is increasing in various fields such as AI, automotive, data centers, storage, and mobile, leading to a growing utilization of PCIe technology.

Qualitas Semiconductor provides PCIe 4.0 PHY IP in the 8 nm FinFET process and has plans to expand to 14 nm, 5 nm, and 4 nm processes. Additionally, Qualitas Semiconductor is developing DSP-based PCIe 6.0 PHY in the 5 nm process.

PCle 6.0

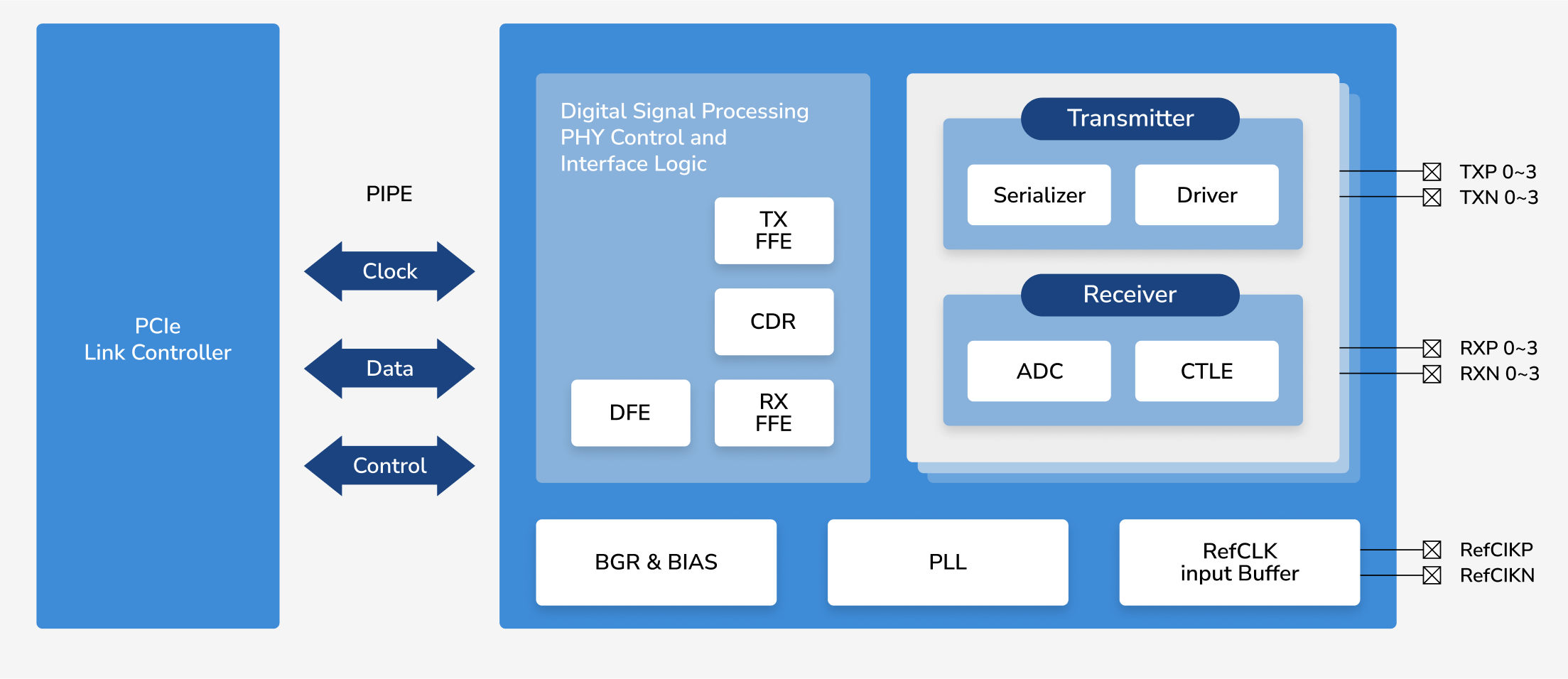

Request DatasheetQualitas' PCIe 6.0 PHY IP consists of hardmacro PMA and PCS compliant with PCIe Base 6.0 specification. This IP offers a cost-effective and low-power solution using FinFET CMOS technology. It includes all ESD I/Os and bump pads and supports extensive built-in self test features such as loopback and scan.

Features

- compliant with PCIe Base 6.0 and PIPE 6.2

- Supports Gen1, Gen2, Gen3, Gen4, Gen5 and Gen6

- Lane configuration

Common (CMN) and 1, 2 or 4 Data Lanes - Supports high-resolution multi-tap FFE in transmitter

- Supports CTLE, DSP-based multi-tap FFE and 1-tap DFE for channel equalization in receiver

- Supports adaptive channel equalization

- Requires a 100 MHz reference clock is required (with support for differential input buffer)

- Built-in self test feature capable of generating and checking PRBS patterns

- PCS included in PHY hardmacro

Tech Specs

| Foundry Node | 5 nm |

|---|---|

| Standard | Under NDA |

| Max. datarate | |

| Status |

PCle 4.0

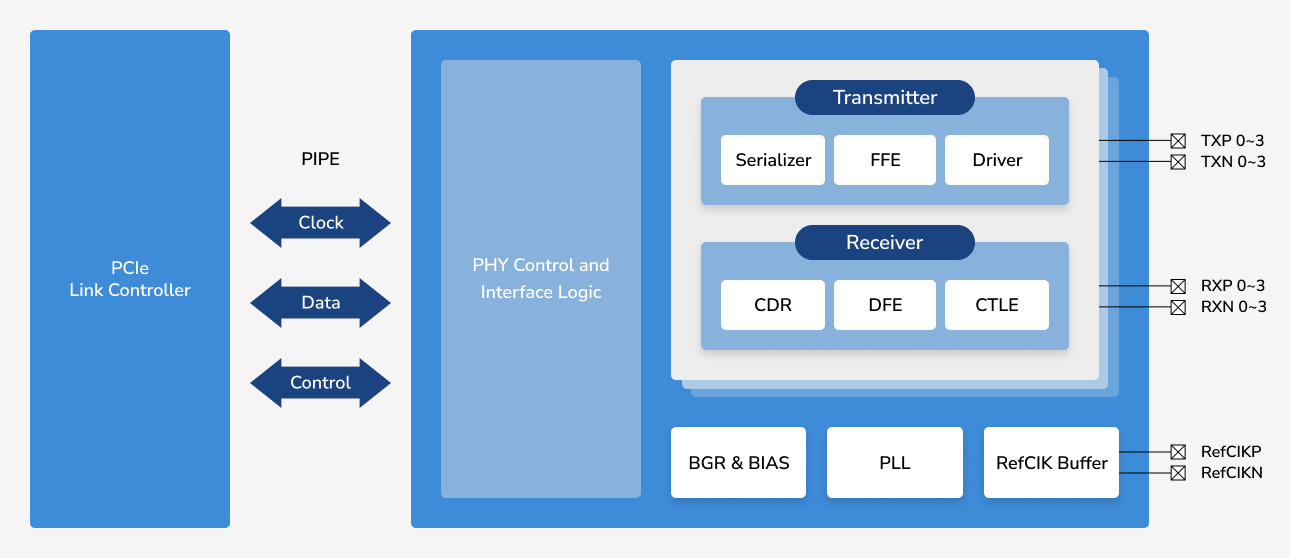

Request DatasheetQualitas' PCIe 4.0 PHY IP consists of hardmacro PMA and softmacro PCS compliant with PCIe Base 4.0 specification. This IP offers a cost-effective and low-power solution using FinFET CMOS technology. It includes all ESD I/Os and bump pads and supports extensive built-in self test features such as loopback and scan.

Features

- compliant with PCIe Base 4.0 and PIPE 4.4.1 specification

- Supports Gen1, Gen2, Gen3 and Gen4

- Lane configuration

Common (CMN) and 1, 2 or 4 Data Lanes - Supports both aggregation and bifurcation modes (5nm PCIe 4.0 PHY only)

4-Lane PHY: 4-Lane aggregation or 2-Lane/2-Lane bifurcation

2-Lane PHY: 2-Lane aggregation or 1-Lane/1-Lane bifurcation - Supports high-resolution multi-tap FFE in transmitter

- Supports CTLE and 5-tap DFE for channel equalization in receiver

- Supports adaptive channel equalization

- Requires a 100 MHz reference clock is required (with support for differential input buffer)

- Built-in self test feature capable of generating and checking PRBS patterns

- Compatible PCS is supports in softmacro form

Tech Specs

| Foundry Node | 8 nm | 5 nm |

|---|---|---|

| Standard | Under NDA | |

| Max. datarate | ||

| Status | ||